Southbridge (computing)

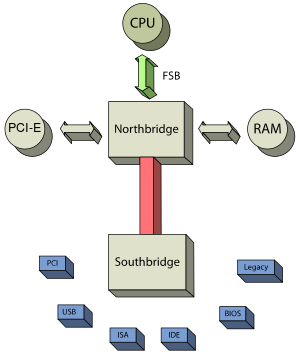

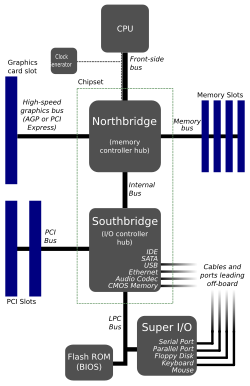

On older personal computer motherboards, the southbridge is one of the two chips in the core logic chipset, handling many of a computer's input/output functions. The other component of the chipset is the northbridge, which generally handles high speed onboard communications.

A southbridge chipset handles functions such as USB, audio, the system firmware, the lower speed PCI/PCIe buses, the IOAPIC interrupt controller, the SATA storage, the historical PATA storage, the NVMe storage, and low speed buses such as ISA, LPC, SPI, and/or eSPI.[1][2] Different combinations of southbridge and northbridge chips are possible,[3] but these two kinds of chips are designed to work together.[citation needed] There is no industry-wide standard for interoperability between different core logic chipset designs. In the 1990s and early 2000s, the interface between a northbridge and southbridge was the PCI bus. As of 2023, the main bridging interfaces used are Direct Media Interface (Intel) and PCI Express (AMD).

The southbridge typically implements the slower capabilities of the motherboard in a northbridge-southbridge chipset computer architecture. In systems with Intel chipsets, the southbridge has been named I/O Controller Hub (ICH) and later replaced by Platform Controller Hub chipsets. In older Intel/AMD architectures the southbridge is usually linked to the northbridge, which in turn connected to the CPU. Circa 2004 and onward Intel architectures started to link southbridge directly to the CPU (.e.g via Direct Media Interface). Through the use of controller-integrated channel circuitry, the northbridge (or CPU itself) can directly link signals from the I/O units to the CPU for data control and access.

As of 2024, most personal computer devices based on Intel or AMD architectures no longer use a set of two chips, and instead have a single chip acting as the 'chipset', for example Intel's Z790 chipset, and a central processing unit.

Current status

[edit]Due to the push for system-on-chip (SoC) processors, modern devices increasingly have the northbridge integrated into the CPU die itself;[further explanation needed] examples are Intel's Sandy Bridge[4] and AMD's Fusion processors,[5] both released in 2011.

With the Intel 5 Series chipset in 2008, the southbridge became redundant and was replaced by the Platform Controller Hub (PCH) architecture introduced. AMD did the same with the release of their first APUs in 2011, naming the PCH the fusion controller hub (FCH), which was only used on AMD's APUs until 2017 when it began to be used on AMD's Zen architecture while dropping the FCH name.

On Intel platforms, all southbridge features and remaining I/O functions are managed by the PCH, which is directly connected to the CPU via the Direct Media Interface (DMI).[6] Intel low-power processors (Haswell-U and onward) and ultra low-power processors (Haswell-Y and onward) also integrate an on-package PCH. Based on its Chiplet design, AMD Ryzen processors also integrated some southbridge functions, such as some USB and SATA/NVMe interfaces.[7]

Etymology

[edit]The name is derived from representing the architecture in the fashion of a map and was first described as such with the introduction of the PCI Local Bus Architecture in 1991. At Intel, the authors of the PCI specification viewed the PCI local bus as being at the very centre of the PC platform architecture (i.e., at the Equator).

The northbridge extends to the north of the PCI bus backbone in support of CPU, memory/cache, and other performance-critical capabilities. Likewise the southbridge extends to the south of the PCI bus backbone and bridges to less performance-critical I/O capabilities such as the disk interface, audio, etc.

The CPU is located at the top of the map at due north. The CPU is connected to the chipset via a fast bridge (the northbridge) located north of other system devices as drawn. The northbridge is connected to the rest of the chipset via a slow bridge (the southbridge) located south of other system devices as drawn.

Although the current PC platform architecture has replaced the PCI bus backbone with faster I/O backbones, the bridge naming convention remains.

Functionality

[edit]

The functionality found in a contemporary southbridge includes:[8][2]

- PCI bus. A south bridge may also include support for PCI-X.

- Low speed PCI Express (PCIe) interfaces usually for Ethernet and NVMe.

- ISA bus or LPC bridge. ISA slots are no longer provided on more recent motherboards. The LPC bridge provides a data and control path to the super I/O (the normal attachment for the PS/2 keyboard and mouse, parallel port, serial port, IR port, and floppy controller).

- SMBus controller.

- DMA controller. The 8237 DMA controller allows ISA or LPC devices direct access to main memory without needing help from the CPU.

- PIC and I/O APIC.

- Mass storage interfaces such as SATA, M.2, and historical PATA. This typically allows attachment of hard drives or SSDs.

- Real-time clock.

- Programmable interval timer.

- High Precision Event Timer.

- ACPI controller or APM controller.

- SPI serial bus mostly used for firmware (e.g., BIOS/UEFI) flash storage access.

- Nonvolatile BIOS memory. The system CMOS (BIOS configuration memory), assisted by battery supplemental power, creates a limited non-volatile storage area for BIOS configuration data.

- Intel HD Audio or AC'97 sound interface.

- USB interfaces.

Optionally, a southbridge also includes support (onboard discrete chip or southbridge-integrated) for Ethernet, Wi-Fi, RAID, Thunderbolt, and Out-of-band management.

See also

[edit]References

[edit]- ^ "What is Southbridge?", Webopedia Computer Dictionary (word definition), 4 November 2002.

- ^ a b Mujtaba, Hassan (2019-09-13). "Intel Z490, H470 Motherboards For 10th Gen Comet Lake-S CPUs Leaked". Wccftech. Retrieved 2020-10-30.

- ^ Chipset: Northbridge and Southbridge, Rigacci.

- ^ Vatto, Kristian. "Why Ivy Bridge is still Quad-core?". Anandtech. Retrieved September 27, 2015.

- ^ Stokes, Jon (11 November 2010). "With Fusion, AMD's devils are in the details". Arstechnica. Retrieved September 27, 2015.

- ^ "Mobile Intel HM57 Express Chipset". Intel. Retrieved 2014-04-21.

- ^ Hagedoorn, Hilbert (23 May 2019). "AMD Ryzen 3000: New Block diagram about PCIe 4.0 on Matisse and X570 chipset". Guru3D.com. Retrieved 2020-06-12.

- ^ What is a chipset?, UK: Misco.

External links

[edit]- "Motherboards & Core-Logic Chipsets: The Deep Stuff > What the North Bridge and South Bridge Do". InformIT. Retrieved November 18, 2010.